為什麼算VSS port到MOS 的bulk pin 腳的點對點電阻 都沒有變化?

例如上圖 designer 想看port VSS 到每一個INV 的電阻, 卻發現xRC 抽出來的電阻, 計算點對點電阻時. port VSS 到 INV1 與 port VSS到INV2 的值相同. 如下圖

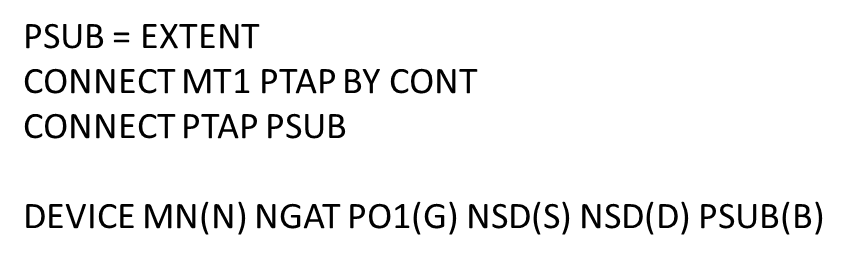

這個原因是因為 NMOS 的BULK pin 腳使用的pin layer 是PSUB

也就是 PSUB 等於所有的layout 面積. MN(N)的bulk pin 使用PSUB

原本xRC 的寄生電阻是diffusion 以上的layer才有定義. 所以所有的MN(N) BULK pin 透過PSUB short 在一起了.

1.

解決的方法是定義PSUB的電阻係數 例如 : RESISTANCE SHEET PSUB [888 0]

點對點電阻值就會有變化, 如下:

由於substrate layer 的電阻計算是另外一個領域, 我們這裡就先以看出port 到bulk pin 點對點電阻b變化為前提.

這邊對於PSUB layer 的電阻準確度 能做的有1. 電阻係數從foundry 取得 2. 如果有需要. 使用2D_FRACTURE 讓PSUB 抽出網狀的電阻.

另外BULK pin 腳定義 又牽扯到LVS rule 的寫法, 只能見招拆招.

(註 : RESISTANCE SHEET 只有xRC 認得. xACT 不會work, 如果遇到xACT 請聯絡原廠的技師了 @@ )

2.

另一種解法是加入 "PEX RESISTANCE OPEN LAYER PSUB" 讓xRC 認為 PSUB 不計算電阻 並且為開路. 在RVE 的P2P 就看不到 bulk pin 腳 . 但是port VSS 到 INV1 INV2 的電阻值差異會顯現出來

留言

張貼留言